If so, what would it be to replace it?

Eric Esteve of SemiWiki just published a blog titled "Goodbye, DDRn Agreement." In the blog, Esteve admits that the blog will be sensational and claims that "the mainstream machines are likely to use DDR4 in the next few years." Intel's recent announcement on March 19 also announced that "the future development of processors will support DDR4." SDRAM". Xilinx is already demonstrating DDR4 support on its new Kintex UltraScale All Programmable device compared to just "announced support" for future products. (See "Ready for DDR4-2400? Need the bandwidth? Need the lower power consumpTIon? Watch this 8-minute video...")

Esteve further confirmed that DDR4 SDRAM will occupy a strong position in the next few years. He wrote: "We can see that DDR4 will be used in the enterprise market in the next two years, and then it will be applied to the desktop computer field. The price of DDR4 memory will be equal to or lower than the price level of DDR3 memory." If foreseen, DDR4 SDRAM will Entering the embedded system is because DDR4 SDRAM will not only provide the highest performance, but the cost per bit will be the lowest.

However, Esteve pointed out that "the '4' in the DDRn series is definitely the latest...", [(original), I think Esteve is referring to the one mentioned in the blog. ]

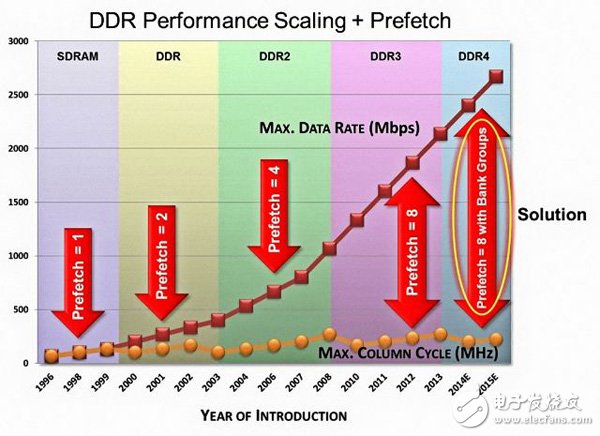

Esteve released the evolution of the DDR standard over the past two decades and the maximum data rate:

Which products will replace DDR? Esteve also made this: "The most promising is based on high-speed serial SerDes products, clock recovery can simplify SoC and board-level implementation." This type of memory sample has emerged, called hybrid memory cube (Hybrid Memory Cube, HMC), the project was sponsored by the Hybrid Memory Cube ConsorTIum. Xilinx, Micron and Open Silicon are the founders of the organization.

The HMC adds a high-speed logic layer between the DRAM and the host processor or SoC. The logic layer manages DRAM so that memory runs through the system over four high-speed serial links, each of which requires 16 high-speed serial Transceivers (64 transceivers when fully connected). The SerDes port on Xilinx Virtex-7 FPGAs fully supports HMC 10Gbps and 12.5Gbps transceiver rates. Up to 96 GTH transceivers per device are set up, making it easy for Xilinx 7 Series FPGAs to easily use the high bandwidth of HMC devices. The GTH transceiver technology in Xilinx UltraScale FPGAs utilizes 64 transceivers to extend the HMC interface bandwidth to 15Gbps. Micron's first commercial 2Gbyte HMC with 160 GB/s memory bandwidth is now available.

(Note: In February of this year, HMC released its first draft of the second generation (Gen2) specification to its application members, including Xilinx, to support double rate. At the press conference, Hugh Durdan, vice president of product and solution sales for Xilinx, pointed out "The UltraScale devices currently shipping are designed to support this specification, reducing risk and speeding time-to-market for high-bandwidth applications."

Similarly, the MoSys Bandwidth Engine 2 is a device that adds fast access memory to systems using multiple high-speed serial channels to achieve a total transfer rate of 250Gbps (see “MoSys Bandwidth Engine 2 adds “Go Juice†to Kintex UltraScale FPGA). Via mulTIple 15.625Gbps lanes at ....")

There is no sign that the new DDR4 memory interface is in a crisis of disappearing. Eric Esteve pointed out that DDR4 SDRAM will continue to be popular for several years and will continue to expand its application in the short and medium term.

A new memory interface will definitely appear. Thanks to the features of the Xilinx 7 Series and the UltraScale device All Programmable (the flexibility and programmability of I/O, and the ability to instantiate any necessary memory controller into the device's programmable logic architecture), let any new Memory can be quickly applied to the system.

Also, you need to tell everyone that Xilinx has a Memory Interface Generator (MIG) tool that automatically generates controllers and PHYs for multiple general-purpose memory interfaces and those that are designed for hybrid interfaces (such as having to control multiple memories on a single device). The following is a short video explaining the MIG tool:

Oculink cable is a high-speed, high-density interconnect cable used in computer systems, specifically for connecting graphics cards or other peripheral devices to the motherboard.It allows for faster data transfer rates and improved performance compared to traditional cables.Oculink cable has amount of advantages including High Bandwidth,Low Latency,Compact and Lightweight and Reliable Connection,etc.

Applications

VR Gaming

VR Content Creation

Medical Training and Simulation

Industrial Design and Engineering

Education and Research

sff 8611,sff 8611 cable,oculink connector,oculink adapter,oculink to sas

Dongguan Aiqun Industrial Co.,Ltd , https://www.gdoikwan.com